片上網(wǎng)絡(luò)賦能 面向5G與數(shù)據(jù)中心的新型FPGA SmartNIC架構(gòu)設(shè)計與技術(shù)開發(fā)

在5G網(wǎng)絡(luò)與超大規(guī)模數(shù)據(jù)中心快速發(fā)展的時代,對網(wǎng)絡(luò)接口卡(NIC)的處理能力、靈活性及能效提出了前所未有的要求。傳統(tǒng)基于固定功能ASIC或通用CPU的智能網(wǎng)卡(SmartNIC)方案,往往在性能、功耗與可編程性之間難以取得理想平衡。本文將探討一種采用片上網(wǎng)絡(luò)(Network-on-Chip, NoC)作為核心互連架構(gòu)的新型FPGA SmartNIC設(shè)計方案,闡述其如何通過軟硬件協(xié)同技術(shù)開發(fā),賦能下一代5G網(wǎng)絡(luò)與數(shù)據(jù)中心基礎(chǔ)設(shè)施。

一、 架構(gòu)設(shè)計:NoC為核心的系統(tǒng)級集成

新型FPGA SmartNIC的設(shè)計核心在于利用FPGA的可編程邏輯資源,構(gòu)建一個以可配置、高帶寬、低延遲的片上網(wǎng)絡(luò)為骨干的異構(gòu)計算系統(tǒng)。該架構(gòu)通常包含以下關(guān)鍵組件:

- 高速網(wǎng)絡(luò)接口單元:集成支持25G/100G/400G以太網(wǎng)、PCIe Gen4/Gen5甚至CXL協(xié)議的高速物理層與控制器,作為數(shù)據(jù)進出芯片的物理通道。

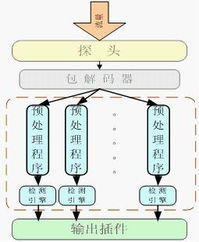

- 可編程數(shù)據(jù)處理流水線:由多個專用處理引擎(如可編程解析器、分類器、查找引擎、加解密引擎、壓縮/解壓引擎)組成,通過NoC互連,實現(xiàn)網(wǎng)絡(luò)數(shù)據(jù)包的線速處理與協(xié)議卸載(如OVS、VXLAN、TCP/IP、RoCE等)。

- 異構(gòu)計算集群:集成多個硬核或軟核處理器(如Arm Cortex-A系列)、AI加速單元(如用于流量預(yù)測或安全檢測的NPU/TPU模塊)以及大容量片上緩存,用于執(zhí)行更復雜的控制平面與數(shù)據(jù)平面任務(wù)。

- 片上網(wǎng)絡(luò)(NoC)互連結(jié)構(gòu):這是架構(gòu)的靈魂。它取代了傳統(tǒng)的總線或交叉開關(guān),提供了一個標準化的、可擴展的、支持服務(wù)質(zhì)量(QoS)的片內(nèi)通信基礎(chǔ)設(shè)施。NoC允許上述各組件并行、高效地交換數(shù)據(jù)與控制信息,顯著提升了系統(tǒng)整體吞吐量并降低了通信延遲。

- 高速內(nèi)存與存儲接口:集成HBM2e/HBM3或DDR5內(nèi)存控制器,為數(shù)據(jù)包緩沖、流表存儲和計算中間結(jié)果提供海量、高帶寬的存儲支持。

二、 賦能5G網(wǎng)絡(luò)的關(guān)鍵技術(shù)開發(fā)

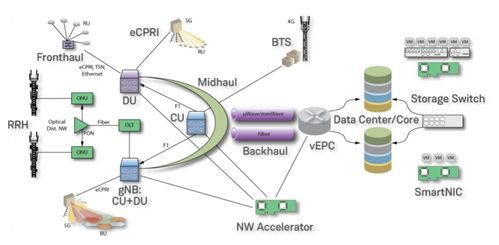

在5G場景下,該架構(gòu)可針對無線接入網(wǎng)(RAN)與核心網(wǎng)(Core)的關(guān)鍵需求進行優(yōu)化:

- 硬件加速的UPF(用戶平面功能):利用FPGA的可編程流水線,實現(xiàn)5G用戶面協(xié)議(GTP-U)的線速處理、QoS流標記與策略執(zhí)行,以及流量統(tǒng)計,滿足邊緣UPF的超低時延與確定性性能要求。

- 前傳/中傳加速:為O-RAN架構(gòu)中的分布式單元(DU)與集中式單元(CU)提供高精度時間同步(如IEEE 1588)、低延遲的以太網(wǎng)封裝/解封裝(如eCPRI)以及安全功能(如MACsec)的硬件卸載。

- 網(wǎng)絡(luò)切片與邊緣計算:通過NoC的虛擬通道與QoS機制,在單張SmartNIC上實現(xiàn)物理資源的邏輯隔離,為不同的網(wǎng)絡(luò)切片提供差異化的數(shù)據(jù)平面處理能力。集成的計算單元可在網(wǎng)絡(luò)邊緣直接處理數(shù)據(jù),減少回傳壓力。

三、 賦能數(shù)據(jù)中心的技術(shù)優(yōu)勢

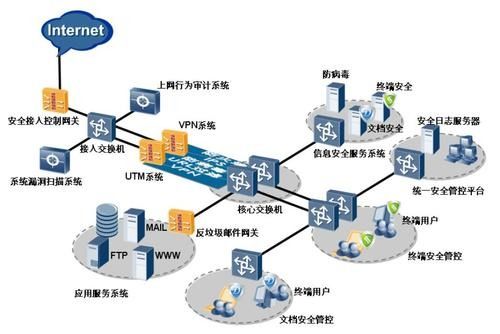

在云數(shù)據(jù)中心內(nèi)部,該設(shè)計方案展現(xiàn)出強大的適應(yīng)能力:

- 可編程的云網(wǎng)絡(luò)虛擬化:完全在硬件層面卸載虛擬交換機(如OVS)、虛擬路由、覆蓋網(wǎng)絡(luò)(VXLAN、Geneve)等復雜功能,釋放主機CPU資源。NoC架構(gòu)使得這些功能的流水線可以靈活組合與更新。

- 存儲與安全卸載:高效卸載NVMe-oF(尤其是基于RoCE的)、數(shù)據(jù)壓縮/解壓、重復數(shù)據(jù)刪除以及傳輸層/應(yīng)用層的加解密(如TLS 1.3)操作,顯著提升存儲訪問性能與安全性。

- 可組合式基礎(chǔ)設(shè)施:作為可編程的硬件底座,能夠根據(jù)工作負載(如AI訓練、大數(shù)據(jù)分析、高性能計算)動態(tài)配置數(shù)據(jù)處理路徑和加速功能,支持更細粒度的資源池化與調(diào)度。

- 增強的遙測與可觀測性:在數(shù)據(jù)路徑中無縫集成帶內(nèi)網(wǎng)絡(luò)遙測(如INT)探針,以納秒級精度收集網(wǎng)絡(luò)狀態(tài)信息,為自動化運維和性能診斷提供數(shù)據(jù)支撐。

四、 軟硬件協(xié)同開發(fā)挑戰(zhàn)與趨勢

實現(xiàn)這一先進設(shè)計方案,需要深度的軟硬件協(xié)同技術(shù)開發(fā):

- 硬件開發(fā):涉及高級別綜合(HLS)或基于SystemVerilog/UVM的RTL設(shè)計,以構(gòu)建高效、可重用的NoC IP與處理引擎。需充分考慮時序收斂、功耗優(yōu)化與物理布局規(guī)劃。

- 軟件開發(fā):需要提供完善的驅(qū)動、API、管理框架(如基于DPDK、SPDK、P4)以及運行時環(huán)境,允許開發(fā)者以高級語言(如C、P4)描述和部署網(wǎng)絡(luò)功能,而無需深入底層硬件細節(jié)。

- 系統(tǒng)集成與驗證:構(gòu)建從模塊級到系統(tǒng)級的仿真與驗證平臺,確保功能正確性、性能達標及與主機系統(tǒng)(服務(wù)器)的穩(wěn)定協(xié)同。

隨著CXL協(xié)議的普及和計算-存儲-網(wǎng)絡(luò)進一步融合,基于NoC的FPGA SmartNIC有望演進為更通用的異構(gòu)加速平臺,通過統(tǒng)一的互連協(xié)議(如CXL.io/CXL.mem)更緊密地集成到系統(tǒng)架構(gòu)中,成為構(gòu)建高性能、高效率、自適應(yīng)數(shù)據(jù)中心和5G/6G網(wǎng)絡(luò)的核心基石。

結(jié)論

采用片上網(wǎng)絡(luò)架構(gòu)的新型FPGA SmartNIC,通過其卓越的可編程性、高性能互連與異構(gòu)集成能力,為5G網(wǎng)絡(luò)和數(shù)據(jù)中心提供了高度靈活且高效的硬件加速解決方案。它不僅解決了當前網(wǎng)絡(luò)基礎(chǔ)設(shè)施面臨的性能瓶頸與能效挑戰(zhàn),更通過開放的軟硬件生態(tài),為持續(xù)演進的新協(xié)議、新應(yīng)用提供了快速部署的路徑,是推動下一代信息基礎(chǔ)設(shè)施創(chuàng)新的關(guān)鍵技術(shù)之一。

如若轉(zhuǎn)載,請注明出處:http://www.k3553.cn/product/91.html

更新時間:2026-04-08 14:23:59